My podcast guest this week is Jan Zimmerman from TEWS Technologies. Jan and I are talking all about VITA 93 – a new QMC mezzanine card standard and why scalability, modularity and flexibility are central elements of this new standard. Jan and I also discuss the unique I/O capabilities of QMCs and how TEW Technologies is furthering innovation in this arena.

… Read More → "Scalability, Modularity, Flexibility with QMCs and VITA 93"

“Good grief, Charlie Brown!” I just exclaimed upon realizing that I’ve hit another 100-column milestone (including this one) here on EE Journal. That makes 400 columns since I joined the community.

As my columns average around 1,500 words apiece, that’s a whopping 600,000 words—each one handpicked at the crack of dawn whilst still glistening with the morning dew, fresh, fragrant, and … Read More → "WTW (“What the What”)? Another 100 Mindboggling Columns!"

I’m a weak-willed man. I was fully intending to write this column on the topic of simulating radio frequency (RF) designs and devices, including communications and radar systems, when… SQUIRREL!!!

To set the scene and ensure we’re all tap-dancing to the same skirl of the bagpipes—as I previously mentioned in my Read More → "Remarkable Rotary Dial Delights"

My mission today is to inform you about a university course that is no longer offered and a master’s degree program that is not yet available. Intrigued? Read on…

To set the scene, first let me remind you that I originally hail from England. I started at Sheffield Polytechnic (now Sheffield Hallam University) in the summer of 1975. You can read more about … Read More → "Teaching AI to Semiconductor Students, Engineers, and Fabs"

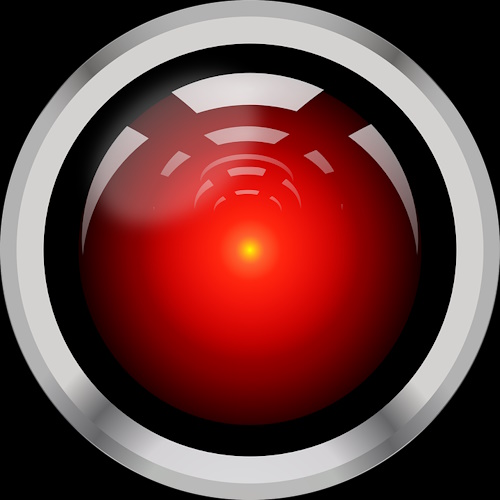

Recently, I re-watched the epic science fiction movie, 2001: A Space Odyssey. Although this film was released in 1968, I don’t think I saw it on the big screen until 1969, when I was 12 years old. I know that by the time I watched the film, I’d already read the book, for which I was very grateful, because that’s pretty much key to understanding what’s going on in the first part of the film. …

Read More → "You May Scoff, But AI-Powered PCB Layout Is Really Real"